大解説! “Fiji”と“HBM”と“Fury”の先進性を知る:キーナンバー“4096”の意義を問う(4/4 ページ)

DirectX 12に最適化されたアーキテクチャ強化

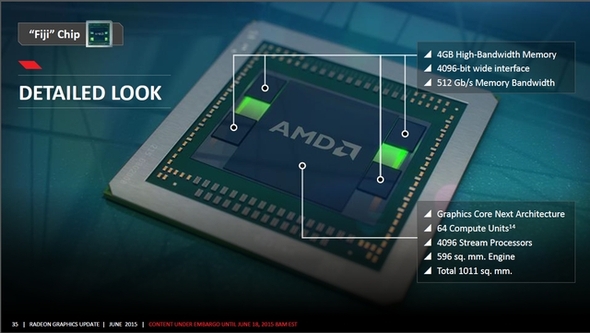

一方、Fijiのアーキテクチャは、Radeon R9 285で採用した“Tonga”コアや、最新APU“Carrizo”と同じ世代の第3世代のGCN(Graphics Core Next)アーキテクチャとなる。とはいえ、公開されたブロックダイヤグラムを見ると、メモリコントローラの部分を除けば、従来の“Hawaii”コアと大差ない構造にみえる。プロセスルールも、従来同様TSMCの28ナノメートルを採用し、596平方ミリのダイサイズに89億トランジスタを集積した。

従来のHawaiiコアが438平方ミリのダイサイズに62億トランジスタを集積していたことと比べると、ダイサイズは35%強大きくなり、そこに45%弱多いトランジスタを詰め込んでいることになる。その大半は、Radeonコアとも呼ばれるStreaming Processor 16基を束ねるCompute Unitの強化に費やし、Hawaiiの44基から64基に増え、Streaming Processorの数も2816基から4096基へと強化した。ROPとも呼ぶレンダーバックエンドは、16基のCUをひとまとめとしたAMDがShader Engineと呼ぶクラスタあたり4基で、4つのShader Engine合計で16基、1基あたり4ピクセルの出力が可能なため、GPUコア全体では64ピクセルの出力をサポートする。

メモリコントローラは、64ビット GDDR5メモリコントローラが8基という構成から、1024ビット(128ビット×8チャネル) HBMコントローラが4基(ブロック図的には512ビットが8基に描いている)に変更し、トランジスタ数の削減に大きく寄与したと、マクリ氏は説明する。また、クドリ氏は、CU数を増やしたこともあり、2次キャッシュ容量はHawaiiの1Mバイトから、Fijiでは2Mバイトに強化していることや、Tongaで追加したピクセルを可逆圧縮することで実行メモリ帯域を向上させるDelta Color Compression機能も搭載していることを明らかにしている。

さらに、クドリ氏はDirectX 12ではより多くのスレッドが走るようになるため、ジオメトリ性能の向上を図っているとして、より効率的な描画処理を可能にするディスパッチ・ドローなどの強化を図っていると明言した。GPUを使った汎用演算などの制御を行なうACE(Asynchronus Compute Engine)は、従来どおり8基のままだが、DirectX 12では、グラフィックス描画のみならず、物理演算など数多くのタスクが発生するため、複数の演算処理を並列で行なえるようにする非同期演算性能が重要になるとして、同機能の効率も高めている。その一方で、従来通りの28ナノメートルプロセスルールを使いながら、消費電力を抑えるため、より積極的なクロック制御を行なうことで、Hawaiiコアと比べて、1.5倍の消費電力あたりパフォーマンスを実現可能にしたと訴えた。

関連記事

“Fiji”と“HBM”の実力を「Radeon R9 Fury X」で知る

“Fiji”と“HBM”の実力を「Radeon R9 Fury X」で知る

AMDの新世代GPU“Fiji”を搭載したグラフィックスカードの最上位モデルでベンチマークテストを走らせる。AMDの新技術は“GTX 980 Ti”を圧倒できるのか? 超品薄なFury Xに「アキバをさまよう人がたくさん出そう」の声

超品薄なFury Xに「アキバをさまよう人がたくさん出そう」の声

Radeon最上位の「R9 Fury X」搭載カードが登場して大きな反響を呼んだが、入荷数が少なく競争率が跳ね上がっている。需要と供給が釣り合うのはいつ? HBMを導入するとこんなにコンパクト──AMD、Fijiの実物を日本で公開

HBMを導入するとこんなにコンパクト──AMD、Fijiの実物を日本で公開

Radeon R9 Fijiの登場を記念したユーザーイベントが秋葉原で開催。グラフィックスメモリをGPUに統合したFijiのすごさを日本のユーザーにアピールした。 AMD、“Fiji”搭載「Radeon R9 Furyシリーズ」の仕様と性能を公開

AMD、“Fiji”搭載「Radeon R9 Furyシリーズ」の仕様と性能を公開

4K設定におけるゲームタイトルベンチマークテストではGeForce GTX 980 Tiに対して有利なスコアを示している(AMD調べ)。 E3現地で“Fiji”世代「Radeon R9 Fury X」「Radeon R9 Nano」の実物をチェックする

E3現地で“Fiji”世代「Radeon R9 Fury X」「Radeon R9 Nano」の実物をチェックする

米AMDが発表した次世代GPU「Radeon R9 Fury」ファミリーの姿とHBMをはじめとする新技術の概要を会場から報告する。 AMD、HBM採用の“Fiji”世代GPU「Radeon R9 Fury」シリーズをE3で発表

AMD、HBM採用の“Fiji”世代GPU「Radeon R9 Fury」シリーズをE3で発表

出荷開始は6月24日から。液冷ユニットを搭載した最上位モデル「R9 Fury X」や6インチとコンパクトサイズの「R9 Fury Nano」などが登場する 「Zen」とHBMで大きく変わるAMDのCPUとGPU

「Zen」とHBMで大きく変わるAMDのCPUとGPU

AMDはCPUロードマップを大幅に変更。開発の主軸をハイパフォーマンスモデルへとシフトする。GPUとARMベースプロセッサも開発計画を大きく変えた。 TSUKUMO、ゲーミングPC「G-GEAR」のBTOオプションに最新GPU“Radeon R9 390X”を追加

TSUKUMO、ゲーミングPC「G-GEAR」のBTOオプションに最新GPU“Radeon R9 390X”を追加

Project Whiteは、同社製のゲーミングデスクトップPC「G-GEAR」シリーズのBTOオプションにRadeon R9 390X搭載グラフィックスカードを追加した。 サードウェーブデジノス、ゲーミングPC「GALLERIA」にRadeon R9 Fury X搭載のハイスペックモデルを追加

サードウェーブデジノス、ゲーミングPC「GALLERIA」にRadeon R9 Fury X搭載のハイスペックモデルを追加

サードウェーブデジノスは、AMD製最新GPUとなるRadeon R9 Fury X搭載カード採用ゲーミングPC「GALLERIA ZKR」を発表した。 GTA Vが4K&最高画質で快適に動く! 「GeForce GTX 980 Ti」の“微妙”な立ち位置を考察する

GTA Vが4K&最高画質で快適に動く! 「GeForce GTX 980 Ti」の“微妙”な立ち位置を考察する

GeForce GTX 980の1つ上にある「GeForce GTX 980 Ti」が登場。“Ti”に期待する一方で“微妙”な仕様が気にところだ。果たして実力はいかほどなのか? NVIDIA最高級GPU「GeForce GTX TITAN X」の“150%”な実力を試す

NVIDIA最高級GPU「GeForce GTX TITAN X」の“150%”な実力を試す

NVIDIAがMaxwell世代のシングルGPUで最上位モデルとなる「GeForce GTX TITAN X」を発表した。GeForce GTX 980を超える最強Maxwellの実力を検証しよう。

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- ワコムが有機ELペンタブレットをついに投入! 「Wacom Movink 13」は約420gの軽量モデルだ (2024年04月24日)

- わずか237gとスマホ並みに軽いモバイルディスプレイ! ユニークの10.5型「UQ-PM10FHDNT-GL」を試す (2024年04月25日)

- 「社長室と役員室はなくしました」 価値共創領域に挑戦する日本IBM 山口社長のこだわり (2024年04月24日)

- QualcommがPC向けSoC「Snapdragon X Plus」を発表 CPUコアを削減しつつも圧倒的なAI処理性能は維持 搭載PCは2024年中盤に登場予定 (2024年04月25日)

- 「Surface Go」が“タフブック”みたいになる耐衝撃ケース サンワサプライから登場 (2024年04月24日)

- 16.3型の折りたたみノートPC「Thinkpad X1 Fold」は“大画面タブレット”として大きな価値あり (2024年04月24日)

- AI PC時代の製品選び 展示会「第33回 Japan IT Week 春」で目にしたもの AI活用やDX化を推進したい企業は要注目! (2024年04月25日)

- あなたのPCのWindows 10/11の「ライセンス」はどうなっている? 調べる方法をチェック! (2023年10月20日)

- エレコム、10GbEポートを備えたWi-Fi 7対応無線LANルーター (2024年04月25日)

- アドバンテック、第14世代Coreプロセッサを採用した産業向けシングルボードPC (2024年04月24日)