徐々に見えてくるNehalem──8Mバイトの3次キャッシュは「みんなで使う」:元麻布春男のWatchTower (2/2 ページ)

DDR3-1333を3チャネルでサポートするNehalem

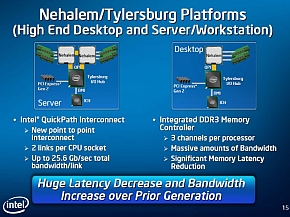

今回のセッションでは、Nehalemが内蔵するメモリコントローラが3チャネルのメモリバスをサポートしたDDR3対応のものであることが明らかにされた。レジスタ付きメモリとアンバッファドメモリの両方に対応し、メモリチャネルあたり最大3つのDIMMソケットをサポートする。ただし、3DIMMのサポートには動作クロックなどの制約があるので、実際には1チャネルあたり2つのDIMMになるのではないかと思われる。

Nehalemでは、メモリバスクロックが高速になるためDIMMソケットは1チャネルにつき1つになるではないか、とも言われていたが、とりあえずマルチチャネルという現状は維持された格好だ。現在、多くのユーザーはメモリを2本単位で購入しているが、Nehalemでは(バスクロックの制約が解決すれば)3本単位で購入することになるだろう。メモリメーカーが喜びそうな話だ。

以前この連載でも紹介したNehalemのプラットフォーム(3月上旬に開かれたInvestor Meetingで披露されたもの)では、チップセットに「システムコントローラ」という名称が使われ、メモリにも「DDR2」という記載があった。今回紹介されたNehalemではチップセットのところに「Tylersburg I/O Hub」という記載があり、明らかにプラットフォームとして異なる。DPのプラットフォームと基本構成が同じであることからも、明らかにハイエンド向けだ。しかし、Nehalem世代がすべてDDR3のみになるかどうかは、メモリ価格の動向も含め、現時点では断言できない。

Quick Path Interconnectは、以前CSI(Common System Interface)という開発コード名で呼ばれていた。シリアルバス技術を用いたものだと言われているが、レーン数や構成が対称か非対称かは明らかにされていない。ただ、25.6Gbpsのトータル帯域を提供とされており、1クロックあたり4バイト(32ビット)の転送が可能なようだ。

Nehalemのキャッシュ構成は「専用の256K」に「共有の8M」

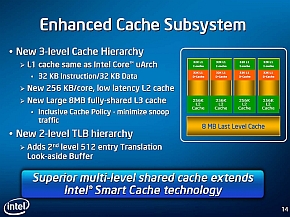

今回のセッションでNehalemについて明らかにされたことの1つは、Nehalemのキャッシュ構成だ。Nehalemコアは従来と同じ32Kバイト+32Kバイトの1次キャッシュに加え、コアごとに独立した256Kバイトの2次キャッシュ、ダイにあるすべてのコアで共有する最大8Mバイトの3次キャッシュを備える。

「Investor Meeting」で示された資料では、3次キャッシュが2コア単位で分断されていたが、あれは物理的な構成を反映しているものの、論理的な構成は反映していないものだったようだ。キャッシュはすべてインクルーシブキャッシュ(上位レベルのキャッシュの内容はすべて下位レベルのキャッシュにも存在する)で、共有3次キャッシュをミスした場合に備えてほかのコアの2次キャッシュや1次キャッシュをスヌープする必要はない。IntelはNehalemのキャッシュについて、複数レベルの「シェアードキャッシュ」という表現を用いてきたが、「複数レベル」はキャッシュにかかる形容詞で、シェアードにかかる形容詞ではなかったようだ。

Nehalemと、それに対応するTylersburgプラットフォームの構成。Nehalemに実装されるメモリコントローラはDDR3に対応し、メモリバスは3チャネルをひとまとまりとして扱える。CPUと接続するI/O HubのバスはFSBからQPIに移行する予定だ

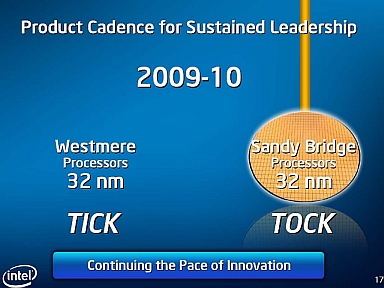

Nehalemと、それに対応するTylersburgプラットフォームの構成。Nehalemに実装されるメモリコントローラはDDR3に対応し、メモリバスは3チャネルをひとまとまりとして扱える。CPUと接続するI/O HubのバスはFSBからQPIに移行する予定だ先ほども述べたように、Nehalemは2008年の終わりあたりにデビューするものと思われるが、本格的な出荷とラインアップの展開は2009年になるだろう。そして2009年末には初の32ナノメートルプロセスルールを採用する「Westmer」が、Nehalemのシュリンク版として登場する。2010年に登場する「Sandy Bridge」が次の新マイクロアーキテクチャというわけだが、今回Sandy Bridgeが搭載する新しい命令として、Intel AVX(Advanced Vector Extensions)が発表された。AVXでは命令のデータ長が、SSEの128ビットから256ビットに拡張され、オペランドが2から3になるといった拡張が施されるという。このAVXについては上海で行われるIDFでもう少し明らかにされる見込みだ。(本文中にあるCPUを表すアルファベット表記の固有呼称は開発コート名である)

Nehalemの登場で45ナノプロセスにおける“Tick Tock”は完了する。次の32ナノプロセス“Tick Tock”は、2009年のWestmere、そして2010年の“Sandy Bridge”が予定されている

Nehalemの登場で45ナノプロセスにおける“Tick Tock”は完了する。次の32ナノプロセス“Tick Tock”は、2009年のWestmere、そして2010年の“Sandy Bridge”が予定されている関連記事

インテルの次世代プラットフォームを考える

インテルの次世代プラットフォームを考える

Intel 4シリーズチップセットやCentrino2と、徐々にではあるがインテルの次世代プラットフォームが姿を現しつつある。その概要をまとめた。 インテルの次世代最高級プラットフォーム「Skulltrail」で「8コア」の破壊力を知る

インテルの次世代最高級プラットフォーム「Skulltrail」で「8コア」の破壊力を知る

“エンスーなゲームユーザー”のための次世代プラットフォームを構成するCPUとマザーボードのパフォーマンスがついに明らかになる。「8コアCPU」がたたき出す最高級の性能やいかに。 インテルは2008年も「革新」

インテルは2008年も「革新」

インテルが年頭記者会見を行い「2008年にインテルが成すべきこと」を披露。会場ではCESに登場した「Menlow」「Canmore」、そして、その先をいく「Moorstown」が展示された。 インテルの2008年マイルストーンは“45ナノ”と“ひまわり”

インテルの2008年マイルストーンは“45ナノ”と“ひまわり”

インテルが45ナノメートルの製造プロセスに対応した「Penryn」ファミリーの新CPU発表会を開催。“性能向上”だけでなく、“クリーンさ”を前面に打ち出した。 北京を旅するなら「Menlow」をお供に──Intel CEOのCES基調講演

北京を旅するなら「Menlow」をお供に──Intel CEOのCES基調講演

Intelの基調講演と聞くと「技術的優位性を力強くアピール」するイメージが強いが、デジタル家電の祭典であるCESでは「分かりやすくて面白い」内容で聴衆を楽しませてくれた。 WiMAXとMoorestownで広がるモバイルデバイスの行動圏

WiMAXとMoorestownで広がるモバイルデバイスの行動圏

IDF 2007の2日めは「モバイル・デイ」がテーマだった。ここでは、ノートPC、UMPC、新しいカテゴリの小型デバイス、そしてWiMAXに関するIntelの発言をまとめていく。 UMPC向けプラットフォーム「Intel Ultra Mobile Platform 2007」を正式発表──チャンドラシーカ氏基調講演

UMPC向けプラットフォーム「Intel Ultra Mobile Platform 2007」を正式発表──チャンドラシーカ氏基調講演

2日間の日程で行われたIDF 2007 Beijingにおいて、最も話題を呼んだのがアナンド・チャンドラシーカ氏による新しいUMPCプラットフォームの発表だ。 Centrino生誕の地、イスラエルのFabに行く(前編)

Centrino生誕の地、イスラエルのFabに行く(前編)

Intelのイスラエル拠点、と聞くと、なにかしら“謎のベール”に閉ざされているようなイメージが(勝手な妄想)。元麻布氏はイスラエルのFabでなにを見たのか。 Centrino生誕の地、イスラエルのFabに行く(後編)

Centrino生誕の地、イスラエルのFabに行く(後編)

イスラエルのインテル拠点を巡礼する元麻布氏。前回訪れた「Haifa Validation Center」を後にして、今回は45ナノプロセスの製造拠点に向かう。 新世代「45ナノ」CPUの実力を「SYSmark2007」で知る──Core 2 Extreme QX9650

新世代「45ナノ」CPUの実力を「SYSmark2007」で知る──Core 2 Extreme QX9650

45ナノプロセスルールの時代がもう目の前まできている。その“Penryn”の性能を新世代のベンチマークでじっくりと確かめてみた。 「Nehalem」が動いたっ!──IDF初日基調講演から

「Nehalem」が動いたっ!──IDF初日基調講演から

年2回の開催から年1回となったIDF(北京は特別版ということで)。そのおかげで内容も充実している。リポート第2弾は「Penryn」「Nehalem」をカバーしよう。 DDR3への移行はいつ?──IDF 2007で読む「メモリ」「ワイヤレス」のトレンド

DDR3への移行はいつ?──IDF 2007で読む「メモリ」「ワイヤレス」のトレンド

大きなインパクトはないものの、細かいアップデート情報で今後のトレンドが把握できた今回のIDF。最後のリポートでは展示会場を中心に紹介したい。 「3.0」世代の新規格が明らかに──IDF 2007基調講演から

「3.0」世代の新規格が明らかに──IDF 2007基調講演から

IDFでは、CPUやプラットフォームに限らない、開発中の新しい技術規格も紹介される。2007年のIDFで取り上げられたのは「USB」「PCI Express」の次世代規格だ。 45ナノメートル以降のプロセス技術をひもとく──マーク・ボーア氏基調講演

45ナノメートル以降のプロセス技術をひもとく──マーク・ボーア氏基調講演

Intel上級フェローのマーク・ボーア氏が、IDF 2007 Beijingで製造プロセス技術の解説を行い、同社の技術的なアドバンテージをアピールした。 Silverthorneは「1ワット2GHz駆動」を目指す

Silverthorneは「1ワット2GHz駆動」を目指す

まもなく始まるISSCC(国際固体回路会議)でIntelは多数の論文を発表する。そのなかには、“Silverthorne”に言及するものも用意される。 CESで「Menlowマシン」をプチプチしました──「韓国」「中国」「台湾」編

CESで「Menlowマシン」をプチプチしました──「韓国」「中国」「台湾」編

2008年のCESでMenlowマシンをプチプチ(ソフトウェアキーボードなので正しくは“ペタペタ”)してニヤニヤしていた記者は東芝だけでは「満腹」にならなかったようだ。 CESで「Menlowマシン」をプチプチしました──東芝編

CESで「Menlowマシン」をプチプチしました──東芝編

2007年のCESで「OQOをプチプチ」していたPC USERの記者が、2008年のCESでは「Menlow」マシンで喜んでいるらしい。- 元麻布春男のWatchTower:バックナンバー

関連リンク

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- 画面を持たない約12gの超軽量ウェルネストラッカー「Google Fitbit Air」 1万6800円で5月26日に発売 (2026年05月07日)

- USB Type-Cの映像出力をワイヤレスでHDMI入力できる「エレコム ワイヤレス HDMI 送受信機セット DH-CW4K110EBK」がセールで1万2580円に (2026年05月08日)

- NAS向け低容量HDD枯渇に「Core Ultra 200S Plus」品薄も――大型連休明けのストレージとメモリ最新動向 (2026年05月09日)

- まるで工芸品な3kg超のアルミ塊! 官能的すぎる“磁気×メカニカル”なキーボード「Lofree Hyzen」を試す (2026年05月07日)

- VAIO事業が絶好調のノジマ、第4四半期の出荷台数は過去最高に 「AI PC」需要で次期も成長を見込む (2026年05月07日)

- 「SwitchBot スマートサーキュレーター(スタンド型)」を試す インテリアになじむ木目調、扇風機の代わりはなる? (2026年05月08日)

- Microsoftが4月度のWindows非セキュリティプレビューパッチを公開/PCI-SIGが次世代規格「PCI Express 8.0」のドラフト版を公開 (2026年05月10日)

- 16型で約1.2kg、USキーボード搭載! こだわり派のあなたに適した「LG gram Pro 16」が33%オフの19万9800円に (2026年05月08日)

- Microsoftが描く「定額+従量課金」のAI新時代と、無制限の“エッジAI”へと向かうWindowsのゆくえ (2026年05月08日)

- モジュール型ミニPC「Khadas Mind」をSurface風に変貌させる拡張ディスプレイ「Mind xPlay」レビュー (2026年05月06日)