Hot Chips 22で示されたAMDの次世代CPU“ブル&ボブ”:元麻布春男のWatchTower(1/3 ページ)

2ソケットサーバに特化した“モジュール化”アーキテクチャ

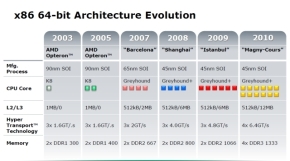

デスクトップPC向けのPhoenom II X6、サーバ向けのOpteron 6100/同 4100は、いずれも2007年に発表された「Barcelona」で採用した「Greyhound」コアの改良型で、2008年の「Shanghai」に採用されたものだ。それからCPUコアの大きな変更は4年近く行われていない。2011年に登場すると予定しているBulldozerとBobcatは、AMDにとって4年ぶりの“新世代”マイクロアーキテクチャというわけだ。

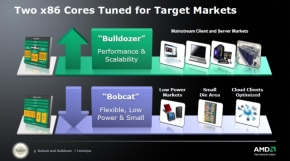

この2つのマイクロアーキテクチャは、それぞれ異なる市場をターゲットにしている。BulldozerはメインストリームのPC、およびサーバ向けとして、性能とスケーラビリティを重視し、BobcatはシンクライアントやNetbook、低価格の超低電圧CPUといった省電力クライアント向けに、省電力とダイサイズ、使い回しの効く柔軟性を実現すべく開発が進められている。想定する市場という意味で、BobcatはインテルのAtom対抗ということにもなる。

Bulldozerの概要が初めて公開されたのは、2009年11月に開催された「Financial Analyst Day 09」であった。Hot Chips 22で公開された情報は、基本的にAnalyst Meeting 09の内容を踏襲しており、新しい内容はそれほど追加されていない。

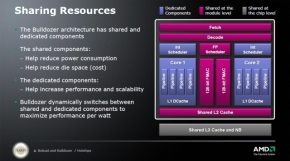

Bulldozerで最大の特徴は、2つの整数演算コアを核とするモジュールを構成単位とすることだ。1つのモジュールには、2組の整数演算コア(4本のパイプラインで構成)と、128ビット長のFMAC(積和演算)をサポートする浮動小数点演算パイプライン2本を含む。

浮動小数点演算パイプラインは、2つのコアで1本づつ占有することも、サイクル単位でどちらかのコアが2本を占有して利用することも可能だとされる。AMDは2009年5月、それまで開発を進めていたSSE5を放棄し、インテルがSandy Bridgeに実装する256ビット長の拡張命令セットであるAVX(Advanced Vector eXtension)をサポートする意向を表明した。浮動小数点演算パイプライン2本を1組として利用することで、AVXのサポートを行うのではないかと考えられる。AMDは、この整数演算コアをCPUコアに相当するものと考えているので、1つのモジュールがデュアルコアということになる。

Bulldozerのアーキテクチャでユニークなのは、複数の演算器を持つにもかかわらず、フェッチやデコーダーは1組しか持たないことだ。コア間で共有する2次キャッシュメモリも含め、モジュール内で多くのリソースが共有される。このように多くを共有する利点として、AMDは消費電力の削減とダイサイズの縮小を挙げている。整数演算ユニットや1次データキャッシュメモリを独立させているのは、ここまで共有にしてしまうと、性能に大きな影響が出るからだろう。

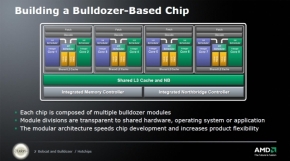

モジュールを構成単位とする目的が明確に見えてくるのは、このモジュールを複数用いてメニーコア化したときだ。Hot Chips22の資料では、Bulldozerベースの8コアチップが示されたが、フェッチやデコードは4組しか存在しない。その分、節約できるダイ面積は大きく、消費電力も減らせるというわけだ。

問題は、このBulldozerコアでAMDがどこへ向かおうとしているのか、ということだ。AMDはHot Chips 22におけるBulldozerの要点として、次の4項目を挙げている。

- Bulldozerは次世代におけるAMDの高性能コアテクノロジー

- この新コアは完全にゼロから新規に開発された

- Bulldozerは2011年のクライアント向けCPUとサーバ向けCPUに導入される見込み

- 現行のMagny-Cours(Opteron 6100番台で採用)と同じ消費電力条件でコア数が33%増加し、性能は50%向上する

これに補足すると、2011年にBulldozerが導入されるのは、Magny-Cours(Opteron 6100番台)後継の「Interlagos」、Lisbon(Opteron 4100番台)後継の「Valencia」、そしてThuban(Phoenom II X6)後継の「Zambezi」と予想されている。2009年秋の時点で、Interlagosは12コア/16コア、Lisbonは6コア/8コア、Zambeziは4コア/8コアとされている(すべて、GLOBALFOUNDRIESの32ナノメートルプロセスルールのSOI High-k/Metal Gateで量産)。

Interlagosは、Lisbonと同等のダイ2枚を1つのパッケージに封入したものと考えられる。この世代におけるBulldozerは純粋なCPUであり、GPU機能を取り込んだAPUにはならない。Magny-Coursの12コアに対し、Interlagosは16コアだから、コア数33%増加というAMDの説明と合致する。

一方、性能の向上は50%とされるが、CPU全体として5割の性能向上としても、コア数が33%増加していることを考えると、1コアあたりの性能向上は12.5%ほどということになる。4年ぶりの新世代コアでコアあたりの性能向上が12.5%というのが高いか低いかは、一概にいえないが、おそらく、ダイ面積の増加を抑えてモジュラー化することで、メニーコアへの展開など柔軟性をもたせた設計であることを踏まえれば、これは大きな性能向上である、とAMDは主張したいのだろう。実際、それは間違ってはいない。

関連キーワード

Bulldozer | Interlagos | Lisbon | Valencia | AMD | Leo | CPU | サーバ | Bobcat | Ontario | Shanghai | Barcelona | 次世代 | サーバ仮想化 | Opteron | Magny-Cours | Zambezi | APU | GLOBALFOUNDRIES | サーバ市場 | メニーコア | サーバ向けプロセッサ | AMD Fusion | AMD Turbo CORE Technology | 元麻布春男 | 自作

Copyright © ITmedia, Inc. All Rights Reserved.

アクセストップ10

- キーボード「FILCO」ブランドのダイヤテックが閉業 4月22日付で (2026年04月24日)

- 大型連休前のアキバは新CPUラッシュ! AMD「Ryzen 9 9950X3D2」とIntel「Core Ultra 5 250K Plus/KF Plus」の気になる在庫状況 (2026年04月25日)

- 持ち運びを極めた超軽量キーボード「ロジクール KEYS TO GO 2」が17%オフの9980円に (2026年04月23日)

- ACアダプター不要の外付けHDD「Seagate One Touch Desktop External Hard Drive」を試す 超大容量で配線スッキリ (2026年04月24日)

- Windows 11の使い勝手はどう変わる? 「Copilot」名称外しやInsider Program再編に見るMicrosoftの本気度 (2026年04月24日)

- 強力なドッキングステーション「Anker PowerExpand Elite 13-in-1 Thunderbolt 3 Dock」が28%オフの2万6490円に (2026年04月23日)

- Microsoftの「12インチSurface Pro」「13インチSurface Laptop」が一部販路で値上げ 直販では4万6200円増しに (2026年04月23日)

- 部屋の雰囲気を一瞬で変えられる「SwitchBot RGBIC フロアライト」が15%オフの7633円に (2026年04月24日)

- Microsoftの新日本語IME「Copilot Keyboard」が正式版に “お前を消す方法”で有名なキャラ「カイル」も追加 (2026年04月23日)

- 「Apple AirPods 4」が20%オフの2万3798円に (2026年04月24日)